Instructions

Objective

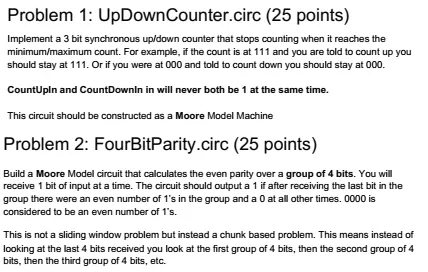

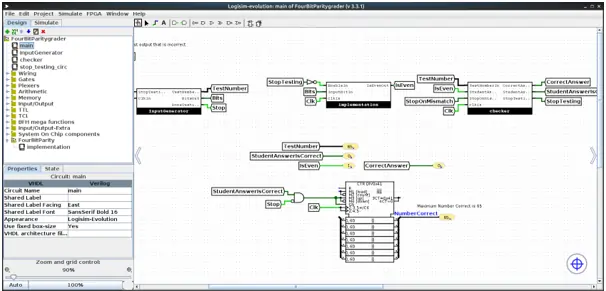

Write a program to design a circuit in LogSim for a 4 bit parity circuit and a vending machine LogSim.

Requirements and Specifications

Source Code

FOUR BIT PARITY

<?xml version="1.0" encoding="UTF-8" standalone="no"?>

<project source="3.3.1" version="1.0">

This file is intended to be loaded by Logisim-evolution (https://github.com/reds-heig/logisim-evolution).

<lib desc="#Wiring" name="0">

<tool name="Splitter">

<a name="appear" val="center"/>

<a name="facing" val="west"/>

<a name="fanout" val="4"/>

<a name="incoming" val="4"/>

</tool>

<tool name="Pin">

<a name="appearance" val="NewPins"/>

</tool>

<tool name="Probe">

<a name="appearance" val="NewPins"/>

</tool>

<tool name="Tunnel">

<a name="width" val="4"/>

</tool>

<tool name="Clock">

<a name="facing" val="north"/>

</tool>

<tool name="Constant">

<a name="value" val="0x3"/>

<a name="width" val="3"/>

</tool>

</lib>

<lib desc="#Gates" name="1">

<tool name="PLA">

<a name="table" val=""/>

</tool>

</lib>

<lib desc="#Plexers" name="2">

<tool name="Multiplexer">

<a name="enable" val="false"/>

</tool>

<tool name="Demultiplexer">

<a name="enable" val="false"/>

</tool>

</lib>

<lib desc="#Arithmetic" name="3"/>

<lib desc="#Memory" name="4">

<tool name="D Flip-Flop">

<a name="appearance" val="logisim_evolution"/>

</tool>

<tool name="T Flip-Flop">

<a name="appearance" val="logisim_evolution"/>

</tool>

<tool name="J-K Flip-Flop">

<a name="appearance" val="logisim_evolution"/>

</tool>

<tool name="S-R Flip-Flop">

<a name="appearance" val="logisim_evolution"/>

</tool>

<tool name="Register">

<a name="appearance" val="logisim_evolution"/>

<a name="width" val="4"/>

</tool>

<tool name="Counter">

<a name="appearance" val="logisim_evolution"/>

</tool>

<tool name="Shift Register">

<a name="appearance" val="logisim_evolution"/>

</tool>

<tool name="Random">

<a name="appearance" val="logisim_evolution"/>

</tool>

<tool name="RAM">

<a name="appearance" val="logisim_evolution"/>

</tool>

<tool name="ROM">

<a name="appearance" val="logisim_evolution"/>

<a name="contents">addr/data: 8 8

0

</a>

</tool>

</lib>

<lib desc="#I/O" name="5"/>

<lib desc="#TTL" name="6"/>

<lib desc="#TCL" name="7">

<tool name="TclGeneric">

<a name="content">library ieee;

use ieee.std_logic_1164.all;

entity TCL_Generic is

port(

--Insert input ports below

horloge_i : in std_logic; -- input bit example

val_i : in std_logic_vector(3 downto 0); -- input vector example

--Insert output ports below

max_o : out std_logic; -- output bit example

cpt_o : out std_logic_Vector(3 downto 0) -- output vector example

);

end TCL_Generic;

</a>

</tool>

</lib>

<lib desc="#Base" name="8">

<tool name="Text Tool">

<a name="font" val="SansSerif plain 12"/>

<a name="halign" val="center"/>

<a name="text" val=""/>

<a name="valign" val="base"/>

</tool>

</lib>

<lib desc="#BFH-Praktika" name="9"/>

<lib desc="#Input/Output-Extra" name="10"/>

<lib desc="#Soc" name="11">

<tool name="Rv32im">

<a name="SocBusSelection" val=""/>

</tool>

<tool name="Nios2">

<a name="SocBusSelection" val=""/>

</tool>

<tool name="SocBus">

<a name="SocBusIdentifier" val="0x00000175848DC786d6e64a7"/>

</tool>

<tool name="Socmem">

<a name="SocBusSelection" val=""/>

</tool>

<tool name="SocPio">

<a name="SocBusSelection" val=""/>

</tool>

<tool name="SocVga">

<a name="SocBusSelection" val=""/>

</tool>

<tool name="SocJtagUart">

<a name="SocBusSelection" val=""/>

</tool>

</lib>

<main name="implementation"/>

<options>

<a name="gateUndefined" val="ignore"/>

<a name="simlimit" val="1000"/>

<a name="simrand" val="0"/>

</options>

<mappings>

<tool lib="8" map="Button2" name="Menu Tool"/>

<tool lib="8" map="Button3" name="Menu Tool"/>

<tool lib="8" map="Ctrl Button1" name="Menu Tool"/>

</mappings>

<toolbar>

<tool lib="8" name="Poke Tool"/>

<tool lib="8" name="Edit Tool"/>

<tool lib="8" name="Wiring Tool"/>

<tool lib="8" name="Text Tool">

<a name="font" val="SansSerif plain 12"/>

<a name="halign" val="center"/>

<a name="text" val=""/>

<a name="valign" val="base"/>

</tool>

<sep/>

<tool lib="0" name="Pin">

<a name="appearance" val="NewPins"/>

</tool>

<tool lib="0" name="Pin">

<a name="appearance" val="NewPins"/>

<a name="facing" val="west"/>

<a name="output" val="true"/>

</tool>

<sep/>

<tool lib="1" name="NOT Gate"/>

<tool lib="1" name="AND Gate"/>

<tool lib="1" name="OR Gate"/>

<tool lib="1" name="XOR Gate"/>

<tool lib="1" name="NAND Gate"/>

<tool lib="1" name="NOR Gate"/>

<sep/>

<tool lib="4" name="D Flip-Flop">

<a name="appearance" val="logisim_evolution"/>

</tool>

<tool lib="4" name="Register">

<a name="appearance" val="logisim_evolution"/>

</tool>

</toolbar>

<circuit name="implementation">

<a name="appearance" val="logisim_evolution"/>

<a name="circuit" val="implementation"/>

<a name="circuitnamedboxfixedsize" val="true"/>

<a name="circuitvhdlpath" val=""/>

<a name="clabel" val=""/>

<a name="clabelfont" val="SansSerif bold 16"/>

<a name="clabelup" val="east"/>

<comp lib="0" loc="(100,420)" name="Tunnel">

<a name="facing" val="east"/>

<a name="label" val="Clk"/>

</comp>

<comp lib="0" loc="(110,320)" name="Tunnel">

<a name="facing" val="east"/>

<a name="label" val="InputBit"/>

</comp>

<comp lib="0" loc="(110,380)" name="Tunnel">

<a name="facing" val="east"/>

<a name="label" val="Enable"/>

</comp>

<comp lib="0" loc="(130,130)" name="Pin">

<a name="appearance" val="NewPins"/>

<a name="label" val="ClkIn"/>

</comp>

<comp lib="0" loc="(130,50)" name="Pin">

<a name="appearance" val="NewPins"/>

<a name="label" val="EnableIn"/>

</comp>

<comp lib="0" loc="(130,80)" name="Pin">

<a name="appearance" val="NewPins"/>

<a name="label" val="InputBitIn"/>

</comp>

<comp lib="0" loc="(160,130)" name="Tunnel">

<a name="label" val="Clk"/>

</comp>

<comp lib="0" loc="(160,50)" name="Tunnel">

<a name="label" val="Enable"/>

</comp>

<comp lib="0" loc="(160,80)" name="Tunnel">

<a name="label" val="InputBit"/>

</comp>

<comp lib="0" loc="(740,190)" name="Pin">

<a name="appearance" val="NewPins"/>

<a name="facing" val="west"/>

<a name="label" val="IsEvenOut"/>

<a name="output" val="true"/>

</comp>

<comp lib="1" loc="(210,420)" name="AND Gate">

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(210,460)" name="AND Gate">

<a name="inputs" val="3"/>

<a name="negate0" val="true"/>

<a name="negate1" val="true"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(210,500)" name="AND Gate">

<a name="inputs" val="3"/>

<a name="negate1" val="true"/>

<a name="negate2" val="true"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(210,540)" name="AND Gate">

<a name="inputs" val="3"/>

<a name="negate0" val="true"/>

<a name="negate2" val="true"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(210,580)" name="AND Gate">

<a name="negate1" val="true"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(210,620)" name="AND Gate">

<a name="inputs" val="3"/>

<a name="negate0" val="true"/>

<a name="negate1" val="true"/>

<a name="negate2" val="true"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(210,660)" name="AND Gate">

<a name="inputs" val="3"/>

<a name="negate1" val="true"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(210,700)" name="AND Gate">

<a name="inputs" val="3"/>

<a name="negate1" val="true"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(220,300)" name="XOR Gate">

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(220,350)" name="XOR Gate">

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(270,310)" name="AND Gate">

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(270,360)" name="AND Gate">

<a name="negate1" val="true"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(300,480)" name="OR Gate">

<a name="inputs" val="4"/>

</comp>

<comp lib="1" loc="(300,600)" name="OR Gate">

<a name="inputs" val="4"/>

</comp>

<comp lib="1" loc="(360,330)" name="OR Gate"/>

<comp lib="1" loc="(600,240)" name="AND Gate">

<a name="inputs" val="3"/>

<a name="size" val="30"/>

</comp>

<comp lib="4" loc="(390,330)" name="Register">

<a name="appearance" val="logisim_evolution"/>

<a name="width" val="1"/>

</comp>

<comp lib="4" loc="(390,450)" name="Register">

<a name="appearance" val="logisim_evolution"/>

<a name="width" val="1"/>

</comp>

<comp lib="4" loc="(390,570)" name="Register">

<a name="appearance" val="logisim_evolution"/>

<a name="width" val="1"/>

</comp>

<wire from="(100,420)" to="(120,420)"/>

<wire from="(110,320)" to="(130,320)"/>

<wire from="(110,380)" to="(370,380)"/>

<wire from="(120,400)" to="(120,420)"/>

<wire from="(120,400)" to="(360,400)"/>

<wire from="(130,130)" to="(160,130)"/>

<wire from="(130,320)" to="(130,370)"/>

<wire from="(130,320)" to="(240,320)"/>

<wire from="(130,370)" to="(130,430)"/>

<wire from="(130,370)" to="(230,370)"/>

<wire from="(130,430)" to="(130,470)"/>

<wire from="(130,430)" to="(180,430)"/>

<wire from="(130,470)" to="(130,510)"/>

<wire from="(130,470)" to="(180,470)"/>

<wire from="(130,50)" to="(160,50)"/>

<wire from="(130,510)" to="(130,550)"/>

<wire from="(130,510)" to="(170,510)"/>

<wire from="(130,550)" to="(130,590)"/>

<wire from="(130,550)" to="(170,550)"/>

<wire from="(130,590)" to="(130,630)"/>

<wire from="(130,590)" to="(170,590)"/>

<wire from="(130,630)" to="(130,670)"/>

<wire from="(130,630)" to="(170,630)"/>

<wire from="(130,670)" to="(130,710)"/>

<wire from="(130,670)" to="(180,670)"/>

<wire from="(130,710)" to="(180,710)"/>

<wire from="(130,80)" to="(160,80)"/>

<wire from="(140,230)" to="(140,310)"/>

<wire from="(140,230)" to="(510,230)"/>

<wire from="(140,310)" to="(140,460)"/>

<wire from="(140,310)" to="(180,310)"/>

<wire from="(140,460)" to="(140,540)"/>

<wire from="(140,460)" to="(170,460)"/>

<wire from="(140,540)" to="(140,570)"/>

<wire from="(140,540)" to="(180,540)"/>

<wire from="(140,570)" to="(140,660)"/>

<wire from="(140,570)" to="(180,570)"/>

<wire from="(140,660)" to="(140,700)"/>

<wire from="(140,660)" to="(170,660)"/>

<wire from="(140,700)" to="(170,700)"/>

<wire from="(150,240)" to="(150,360)"/>

<wire from="(150,240)" to="(490,240)"/>

<wire from="(150,360)" to="(150,410)"/>

<wire from="(150,360)" to="(180,360)"/>

<wire from="(150,410)" to="(150,500)"/>

<wire from="(150,410)" to="(180,410)"/>

<wire from="(150,500)" to="(150,530)"/>

<wire from="(150,500)" to="(170,500)"/>

<wire from="(150,530)" to="(150,620)"/>

<wire from="(150,530)" to="(170,530)"/>

<wire from="(150,620)" to="(150,650)"/>

<wire from="(150,620)" to="(170,620)"/>

<wire from="(150,650)" to="(180,650)"/>

<wire from="(160,250)" to="(160,290)"/>

<wire from="(160,250)" to="(470,250)"/>

<wire from="(160,290)" to="(160,340)"/>

<wire from="(160,290)" to="(180,290)"/>

<wire from="(160,340)" to="(160,450)"/>

<wire from="(160,340)" to="(180,340)"/>

<wire from="(160,450)" to="(160,490)"/>

<wire from="(160,450)" to="(170,450)"/>

<wire from="(160,490)" to="(160,610)"/>

<wire from="(160,490)" to="(180,490)"/>

<wire from="(160,610)" to="(160,690)"/>

<wire from="(160,610)" to="(170,610)"/>

<wire from="(160,690)" to="(180,690)"/>

<wire from="(210,420)" to="(230,420)"/>

<wire from="(210,460)" to="(220,460)"/>

<wire from="(210,500)" to="(230,500)"/>

<wire from="(210,540)" to="(240,540)"/>

<wire from="(210,580)" to="(250,580)"/>

<wire from="(210,620)" to="(220,620)"/>

<wire from="(210,660)" to="(230,660)"/>

<wire from="(210,700)" to="(240,700)"/>

<wire from="(220,300)" to="(240,300)"/>

<wire from="(220,350)" to="(240,350)"/>

<wire from="(220,460)" to="(220,470)"/>

<wire from="(220,470)" to="(250,470)"/>

<wire from="(220,590)" to="(220,620)"/>

<wire from="(220,590)" to="(250,590)"/>

<wire from="(230,420)" to="(230,460)"/>

<wire from="(230,460)" to="(250,460)"/>

<wire from="(230,490)" to="(230,500)"/>

<wire from="(230,490)" to="(250,490)"/>

<wire from="(230,610)" to="(230,660)"/>

<wire from="(230,610)" to="(250,610)"/>

<wire from="(240,500)" to="(240,540)"/>

<wire from="(240,500)" to="(250,500)"/>

<wire from="(240,620)" to="(240,700)"/>

<wire from="(240,620)" to="(250,620)"/>

<wire from="(270,310)" to="(310,310)"/>

<wire from="(270,360)" to="(290,360)"/>

<wire from="(290,350)" to="(290,360)"/>

<wire from="(290,350)" to="(310,350)"/>

<wire from="(300,480)" to="(390,480)"/>

<wire from="(300,600)" to="(390,600)"/>

<wire from="(360,330)" to="(380,330)"/>

<wire from="(360,400)" to="(360,520)"/>

<wire from="(360,400)" to="(390,400)"/>

<wire from="(360,520)" to="(360,640)"/>

<wire from="(360,520)" to="(390,520)"/>

<wire from="(360,640)" to="(390,640)"/>

<wire from="(370,380)" to="(370,500)"/>

<wire from="(370,380)" to="(390,380)"/>

<wire from="(370,500)" to="(370,620)"/>

<wire from="(370,500)" to="(390,500)"/>

<wire from="(370,620)" to="(390,620)"/>

<wire from="(380,330)" to="(380,360)"/>

<wire from="(380,360)" to="(390,360)"/>

<wire from="(450,360)" to="(470,360)"/>

<wire from="(450,480)" to="(490,480)"/>

<wire from="(450,600)" to="(510,600)"/>

<wire from="(470,250)" to="(470,360)"/>

<wire from="(470,250)" to="(570,250)"/>

<wire from="(490,240)" to="(490,480)"/>

<wire from="(490,240)" to="(570,240)"/>

<wire from="(510,230)" to="(510,600)"/>

<wire from="(510,230)" to="(570,230)"/>

<wire from="(600,240)" to="(640,240)"/>

<wire from="(640,190)" to="(640,240)"/>

<wire from="(640,190)" to="(740,190)"/>

</circuit>

</project>

VENDING CIRCUIT

<?xml version="1.0" encoding="UTF-8" standalone="no"?>

<project source="3.3.1" version="1.0">

This file is intended to be loaded by Logisim-evolution (https://github.com/reds-heig/logisim-evolution).

<lib desc="#Wiring" name="0">

<tool name="Splitter">

<a name="appear" val="center"/>

<a name="facing" val="west"/>

<a name="fanout" val="3"/>

<a name="incoming" val="3"/>

</tool>

<tool name="Pin">

<a name="appearance" val="NewPins"/>

</tool>

<tool name="Probe">

<a name="appearance" val="NewPins"/>

</tool>

<tool name="Tunnel">

<a name="width" val="4"/>

</tool>

<tool name="Clock">

<a name="facing" val="north"/>

</tool>

<tool name="Constant">

<a name="value" val="0x3"/>

<a name="width" val="3"/>

</tool>

</lib>

<lib desc="#Gates" name="1">

<tool name="PLA">

<a name="table" val=""/>

</tool>

</lib>

<lib desc="#Plexers" name="2">

<tool name="Multiplexer">

<a name="enable" val="false"/>

</tool>

<tool name="Demultiplexer">

<a name="enable" val="false"/>

</tool>

</lib>

<lib desc="#Arithmetic" name="3"/>

<lib desc="#Memory" name="4">

<tool name="D Flip-Flop">

<a name="appearance" val="logisim_evolution"/>

</tool>

<tool name="T Flip-Flop">

<a name="appearance" val="logisim_evolution"/>

</tool>

<tool name="J-K Flip-Flop">

<a name="appearance" val="logisim_evolution"/>

</tool>

<tool name="S-R Flip-Flop">

<a name="appearance" val="logisim_evolution"/>

</tool>

<tool name="Register">

<a name="appearance" val="logisim_evolution"/>

</tool>

<tool name="Counter">

<a name="appearance" val="logisim_evolution"/>

</tool>

<tool name="Shift Register">

<a name="appearance" val="logisim_evolution"/>

</tool>

<tool name="Random">

<a name="appearance" val="logisim_evolution"/>

</tool>

<tool name="RAM">

<a name="appearance" val="logisim_evolution"/>

</tool>

<tool name="ROM">

<a name="appearance" val="logisim_evolution"/>

<a name="contents">addr/data: 8 8

0

</a>

</tool>

</lib>

<lib desc="#I/O" name="5"/>

<lib desc="#TTL" name="6"/>

<lib desc="#TCL" name="7">

<tool name="TclGeneric">

<a name="content">library ieee;

use ieee.std_logic_1164.all;

entity TCL_Generic is

port(

--Insert input ports below

horloge_i : in std_logic; -- input bit example

val_i : in std_logic_vector(3 downto 0); -- input vector example

--Insert output ports below

max_o : out std_logic; -- output bit example

cpt_o : out std_logic_Vector(3 downto 0) -- output vector example

);

end TCL_Generic;

</a>

</tool>

</lib>

<lib desc="#Base" name="8">

<tool name="Text Tool">

<a name="font" val="SansSerif plain 12"/>

<a name="halign" val="center"/>

<a name="text" val=""/>

<a name="valign" val="base"/>

</tool>

</lib>

<lib desc="#BFH-Praktika" name="9"/>

<lib desc="#Input/Output-Extra" name="10"/>

<lib desc="#Soc" name="11">

<tool name="Rv32im">

<a name="SocBusSelection" val=""/>

</tool>

<tool name="Nios2">

<a name="SocBusSelection" val=""/>

</tool>

<tool name="SocBus">

<a name="SocBusIdentifier" val="0x0000017585BF215876192c6b"/>

</tool>

<tool name="Socmem">

<a name="SocBusSelection" val=""/>

</tool>

<tool name="SocPio">

<a name="SocBusSelection" val=""/>

</tool>

<tool name="SocVga">

<a name="SocBusSelection" val=""/>

</tool>

<tool name="SocJtagUart">

<a name="SocBusSelection" val=""/>

</tool>

</lib>

<main name="implementation"/>

<options>

<a name="gateUndefined" val="ignore"/>

<a name="simlimit" val="1000"/>

<a name="simrand" val="0"/>

</options>

<mappings>

<tool lib="8" map="Button2" name="Menu Tool"/>

<tool lib="8" map="Button3" name="Menu Tool"/>

<tool lib="8" map="Ctrl Button1" name="Menu Tool"/>

</mappings>

<toolbar>

<tool lib="8" name="Poke Tool"/>

<tool lib="8" name="Edit Tool"/>

<tool lib="8" name="Wiring Tool"/>

<tool lib="8" name="Text Tool">

<a name="font" val="SansSerif plain 12"/>

<a name="halign" val="center"/>

<a name="text" val=""/>

<a name="valign" val="base"/>

</tool>

<sep/>

<tool lib="0" name="Pin">

<a name="appearance" val="NewPins"/>

</tool>

<tool lib="0" name="Pin">

<a name="appearance" val="NewPins"/>

<a name="facing" val="west"/>

<a name="output" val="true"/>

</tool>

<sep/>

<tool lib="1" name="NOT Gate"/>

<tool lib="1" name="AND Gate"/>

<tool lib="1" name="OR Gate"/>

<tool lib="1" name="XOR Gate"/>

<tool lib="1" name="NAND Gate"/>

<tool lib="1" name="NOR Gate"/>

<sep/>

<tool lib="4" name="D Flip-Flop">

<a name="appearance" val="logisim_evolution"/>

</tool>

<tool lib="4" name="Register">

<a name="appearance" val="logisim_evolution"/>

</tool>

</toolbar>

<circuit name="implementation">

<a name="appearance" val="logisim_evolution"/>

<a name="circuit" val="implementation"/>

<a name="circuitnamedboxfixedsize" val="true"/>

<a name="circuitvhdlpath" val=""/>

<a name="clabel" val=""/>

<a name="clabelfont" val="SansSerif bold 16"/>

<a name="clabelup" val="east"/>

<comp lib="0" loc="(1170,180)" name="Tunnel">

<a name="facing" val="east"/>

<a name="label" val="Give_Merchandise"/>

</comp>

<comp lib="0" loc="(1170,210)" name="Tunnel">

<a name="facing" val="east"/>

<a name="label" val="Give_Dime"/>

</comp>

<comp lib="0" loc="(1170,240)" name="Tunnel">

<a name="facing" val="east"/>

<a name="label" val="Give_Nickel"/>

</comp>

<comp lib="0" loc="(1180,180)" name="Pin">

<a name="appearance" val="NewPins"/>

<a name="facing" val="west"/>

<a name="label" val="Give_Mechandise_Out"/>

<a name="output" val="true"/>

</comp>

<comp lib="0" loc="(1180,210)" name="Pin">

<a name="appearance" val="NewPins"/>

<a name="facing" val="west"/>

<a name="label" val="Give_Dime_Out"/>

<a name="output" val="true"/>

</comp>

<comp lib="0" loc="(1180,240)" name="Pin">

<a name="appearance" val="NewPins"/>

<a name="facing" val="west"/>

<a name="label" val="Give_Nickel_Out"/>

<a name="output" val="true"/>

</comp>

<comp lib="0" loc="(170,250)" name="Tunnel">

<a name="facing" val="east"/>

<a name="label" val="Enable"/>

</comp>

<comp lib="0" loc="(170,280)" name="Tunnel">

<a name="facing" val="east"/>

<a name="label" val="clk"/>

</comp>

<comp lib="0" loc="(200,110)" name="Pin">

<a name="appearance" val="NewPins"/>

<a name="label" val="QuarterReceivedIn"/>

</comp>

<comp lib="0" loc="(200,140)" name="Pin">

<a name="appearance" val="NewPins"/>

<a name="label" val="DimeReceivedIn"/>

</comp>

<comp lib="0" loc="(200,170)" name="Pin">

<a name="appearance" val="NewPins"/>

<a name="label" val="NickelReceivedIn"/>

</comp>

<comp lib="0" loc="(200,200)" name="Pin">

<a name="appearance" val="NewPins"/>

<a name="label" val="ClkIn"/>

</comp>

<comp lib="0" loc="(200,80)" name="Pin">

<a name="appearance" val="NewPins"/>

<a name="label" val="EnableIn"/>

</comp>

<comp lib="0" loc="(210,110)" name="Tunnel">

<a name="label" val="QuarterReceieved"/>

</comp>

<comp lib="0" loc="(210,140)" name="Tunnel">

<a name="label" val="DimeReceieved"/>

</comp>

<comp lib="0" loc="(210,170)" name="Tunnel">

<a name="label" val="NickelReceieved"/>

</comp>

<comp lib="0" loc="(210,200)" name="Tunnel">

<a name="label" val="clk"/>

</comp>

<comp lib="0" loc="(210,80)" name="Tunnel">

<a name="label" val="Enable"/>

</comp>

<comp lib="0" loc="(220,390)" name="Tunnel">

<a name="facing" val="east"/>

<a name="label" val="QuarterReceieved"/>

</comp>

<comp lib="0" loc="(220,420)" name="Tunnel">

<a name="facing" val="east"/>

<a name="label" val="DimeReceieved"/>

</comp>

<comp lib="0" loc="(220,450)" name="Tunnel">

<a name="facing" val="east"/>

<a name="label" val="NickelReceieved"/>

</comp>

<comp lib="0" loc="(850,410)" name="Tunnel">

<a name="label" val="Give_Merchandise"/>

</comp>

<comp lib="0" loc="(850,560)" name="Tunnel">

<a name="label" val="Give_Dime"/>

</comp>

<comp lib="0" loc="(850,700)" name="Tunnel">

<a name="label" val="Give_Nickel"/>

</comp>

<comp lib="1" loc="(340,1020)" name="AND Gate">

<a name="inputs" val="4"/>

<a name="negate1" val="true"/>

<a name="negate2" val="true"/>

<a name="negate3" val="true"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(340,390)" name="AND Gate">

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(340,430)" name="AND Gate">

<a name="inputs" val="3"/>

<a name="negate1" val="true"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(340,470)" name="AND Gate">

<a name="inputs" val="3"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(340,520)" name="AND Gate">

<a name="inputs" val="4"/>

<a name="negate1" val="true"/>

<a name="negate2" val="true"/>

<a name="negate3" val="true"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(340,590)" name="AND Gate">

<a name="inputs" val="3"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(340,640)" name="AND Gate">

<a name="inputs" val="4"/>

<a name="negate0" val="true"/>

<a name="negate1" val="true"/>

<a name="negate2" val="true"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(340,700)" name="AND Gate">

<a name="inputs" val="4"/>

<a name="negate0" val="true"/>

<a name="negate1" val="true"/>

<a name="negate2" val="true"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(340,760)" name="AND Gate">

<a name="inputs" val="4"/>

<a name="negate1" val="true"/>

<a name="negate2" val="true"/>

<a name="negate3" val="true"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(340,830)" name="AND Gate">

<a name="negate0" val="true"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(340,870)" name="AND Gate">

<a name="inputs" val="3"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(340,910)" name="AND Gate">

<a name="inputs" val="3"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(340,960)" name="AND Gate">

<a name="inputs" val="4"/>

<a name="negate0" val="true"/>

<a name="negate1" val="true"/>

<a name="negate2" val="true"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(430,610)" name="OR Gate">

<a name="inputs" val="4"/>

</comp>

<comp lib="1" loc="(440,450)" name="OR Gate">

<a name="inputs" val="4"/>

</comp>

<comp lib="1" loc="(450,890)" name="OR Gate">

<a name="inputs" val="5"/>

</comp>

<comp lib="1" loc="(670,340)" name="OR Gate">

<a name="inputs" val="3"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(700,380)" name="AND Gate">

<a name="inputs" val="3"/>

<a name="negate1" val="true"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(700,430)" name="AND Gate">

<a name="inputs" val="4"/>

<a name="negate0" val="true"/>

<a name="negate1" val="true"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(700,490)" name="AND Gate">

<a name="inputs" val="4"/>

<a name="negate0" val="true"/>

<a name="negate1" val="true"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(700,540)" name="AND Gate">

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(700,580)" name="AND Gate">

<a name="inputs" val="3"/>

<a name="negate0" val="true"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(700,630)" name="AND Gate">

<a name="inputs" val="3"/>

<a name="negate1" val="true"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(700,670)" name="AND Gate">

<a name="inputs" val="3"/>

<a name="negate1" val="true"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(700,720)" name="AND Gate">

<a name="inputs" val="4"/>

<a name="negate0" val="true"/>

<a name="negate1" val="true"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(700,780)" name="AND Gate">

<a name="inputs" val="4"/>

<a name="negate0" val="true"/>

<a name="negate1" val="true"/>

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(710,330)" name="AND Gate">

<a name="size" val="30"/>

</comp>

<comp lib="1" loc="(780,560)" name="OR Gate"/>

<comp lib="1" loc="(800,410)" name="OR Gate">

<a name="inputs" val="4"/>

</comp>

<comp lib="1" loc="(810,700)" name="OR Gate">

<a name="inputs" val="4"/>

</comp>

<comp lib="4" loc="(490,450)" name="Register">

<a name="appearance" val="logisim_evolution"/>

<a name="width" val="1"/>

</comp>

<comp lib="4" loc="(490,580)" name="Register">

<a name="appearance" val="logisim_evolution"/>

<a name="width" val="1"/>

</comp>

<comp lib="4" loc="(490,860)" name="Register">

<a name="appearance" val="logisim_evolution"/>

<a name="width" val="1"/>

</comp>

<wire from="(1170,180)" to="(1180,180)"/>

<wire from="(1170,210)" to="(1180,210)"/>

<wire from="(1170,240)" to="(1180,240)"/>

<wire from="(170,250)" to="(470,250)"/>

<wire from="(170,280)" to="(460,280)"/>

<wire from="(200,110)" to="(210,110)"/>

<wire from="(200,140)" to="(210,140)"/>

<wire from="(200,170)" to="(210,170)"/>

<wire from="(200,200)" to="(210,200)"/>

<wire from="(200,80)" to="(210,80)"/>

<wire from="(220,390)" to="(260,390)"/>

<wire from="(220,420)" to="(250,420)"/>

<wire from="(220,450)" to="(240,450)"/>

<wire from="(240,1040)" to="(300,1040)"/>

<wire from="(240,300)" to="(240,440)"/>

<wire from="(240,300)" to="(620,300)"/>

<wire from="(240,440)" to="(240,450)"/>

<wire from="(240,440)" to="(310,440)"/>

<wire from="(240,450)" to="(240,480)"/>

<wire from="(240,480)" to="(240,540)"/>

<wire from="(240,480)" to="(310,480)"/>

<wire from="(240,540)" to="(240,600)"/>

<wire from="(240,540)" to="(300,540)"/>

<wire from="(240,600)" to="(240,660)"/>

<wire from="(240,600)" to="(310,600)"/>

<wire from="(240,660)" to="(240,780)"/>

<wire from="(240,660)" to="(310,660)"/>

<wire from="(240,780)" to="(240,840)"/>

<wire from="(240,780)" to="(300,780)"/>

<wire from="(240,840)" to="(240,1040)"/>

<wire from="(240,840)" to="(310,840)"/>

<wire from="(250,1030)" to="(300,1030)"/>

<wire from="(250,310)" to="(250,400)"/>

<wire from="(250,310)" to="(610,310)"/>

<wire from="(250,400)" to="(250,420)"/>

<wire from="(250,400)" to="(310,400)"/>

<wire from="(250,420)" to="(250,530)"/>

<wire from="(250,530)" to="(250,720)"/>

<wire from="(250,530)" to="(300,530)"/>

<wire from="(250,720)" to="(250,770)"/>

<wire from="(250,720)" to="(310,720)"/>

<wire from="(250,770)" to="(250,880)"/>

<wire from="(250,770)" to="(300,770)"/>

<wire from="(250,880)" to="(250,920)"/>

<wire from="(250,880)" to="(310,880)"/>

<wire from="(250,920)" to="(250,1030)"/>

<wire from="(250,920)" to="(310,920)"/>

<wire from="(260,1010)" to="(300,1010)"/>

<wire from="(260,320)" to="(260,390)"/>

<wire from="(260,320)" to="(600,320)"/>

<wire from="(260,390)" to="(260,510)"/>

<wire from="(260,510)" to="(260,750)"/>

<wire from="(260,510)" to="(300,510)"/>

<wire from="(260,750)" to="(260,980)"/>

<wire from="(260,750)" to="(300,750)"/>

<wire from="(260,980)" to="(260,1010)"/>

<wire from="(260,980)" to="(310,980)"/>

<wire from="(270,1000)" to="(310,1000)"/>

<wire from="(270,330)" to="(270,430)"/>

<wire from="(270,330)" to="(590,330)"/>

<wire from="(270,430)" to="(270,470)"/>

<wire from="(270,430)" to="(300,430)"/>

<wire from="(270,470)" to="(270,590)"/>

<wire from="(270,470)" to="(310,470)"/>

<wire from="(270,590)" to="(270,650)"/>

<wire from="(270,590)" to="(310,590)"/>

<wire from="(270,650)" to="(270,710)"/>

<wire from="(270,650)" to="(300,650)"/>

<wire from="(270,710)" to="(270,820)"/>

<wire from="(270,710)" to="(300,710)"/>

<wire from="(270,820)" to="(270,870)"/>

<wire from="(270,820)" to="(300,820)"/>

<wire from="(270,870)" to="(270,910)"/>

<wire from="(270,870)" to="(310,870)"/>

<wire from="(270,910)" to="(270,970)"/>

<wire from="(270,910)" to="(310,910)"/>

<wire from="(270,970)" to="(270,1000)"/>

<wire from="(270,970)" to="(300,970)"/>

<wire from="(280,340)" to="(280,380)"/>

<wire from="(280,340)" to="(580,340)"/>

<wire from="(280,380)" to="(280,420)"/>

<wire from="(280,380)" to="(310,380)"/>

<wire from="(280,420)" to="(280,580)"/>

<wire from="(280,420)" to="(310,420)"/>

<wire from="(280,580)" to="(280,630)"/>

<wire from="(280,580)" to="(310,580)"/>

<wire from="(280,630)" to="(280,690)"/>

<wire from="(280,630)" to="(300,630)"/>

<wire from="(280,690)" to="(280,740)"/>

<wire from="(280,690)" to="(300,690)"/>

<wire from="(280,740)" to="(280,860)"/>

<wire from="(280,740)" to="(310,740)"/>

<wire from="(280,860)" to="(280,950)"/>

<wire from="(280,860)" to="(310,860)"/>

<wire from="(280,950)" to="(300,950)"/>

<wire from="(290,350)" to="(290,460)"/>

<wire from="(290,350)" to="(570,350)"/>

<wire from="(290,460)" to="(290,500)"/>

<wire from="(290,460)" to="(310,460)"/>

<wire from="(290,500)" to="(290,620)"/>

<wire from="(290,500)" to="(310,500)"/>

<wire from="(290,620)" to="(290,680)"/>

<wire from="(290,620)" to="(300,620)"/>

<wire from="(290,680)" to="(290,900)"/>

<wire from="(290,680)" to="(300,680)"/>

<wire from="(290,900)" to="(290,940)"/>

<wire from="(290,900)" to="(310,900)"/>

<wire from="(290,940)" to="(300,940)"/>

<wire from="(340,1020)" to="(370,1020)"/>

<wire from="(340,390)" to="(370,390)"/>

<wire from="(340,430)" to="(360,430)"/>

<wire from="(340,470)" to="(360,470)"/>

<wire from="(340,520)" to="(370,520)"/>

<wire from="(340,590)" to="(380,590)"/>

<wire from="(340,640)" to="(350,640)"/>

<wire from="(340,700)" to="(360,700)"/>

<wire from="(340,760)" to="(370,760)"/>

<wire from="(340,830)" to="(390,830)"/>

<wire from="(340,870)" to="(380,870)"/>

<wire from="(340,910)" to="(350,910)"/>

<wire from="(340,960)" to="(360,960)"/>

<wire from="(350,600)" to="(350,640)"/>

<wire from="(350,600)" to="(380,600)"/>

<wire from="(350,890)" to="(350,910)"/>

<wire from="(350,890)" to="(400,890)"/>

<wire from="(360,430)" to="(360,440)"/>

<wire from="(360,440)" to="(390,440)"/>

<wire from="(360,460)" to="(360,470)"/>

<wire from="(360,460)" to="(390,460)"/>

<wire from="(360,620)" to="(360,700)"/>

<wire from="(360,620)" to="(380,620)"/>

<wire from="(360,900)" to="(360,960)"/>

<wire from="(360,900)" to="(400,900)"/>

<wire from="(370,390)" to="(370,430)"/>

<wire from="(370,430)" to="(390,430)"/>

<wire from="(370,470)" to="(370,520)"/>

<wire from="(370,470)" to="(390,470)"/>

<wire from="(370,630)" to="(370,760)"/>

<wire from="(370,630)" to="(380,630)"/>

<wire from="(370,910)" to="(370,1020)"/>

<wire from="(370,910)" to="(400,910)"/>

<wire from="(380,870)" to="(380,880)"/>

<wire from="(380,880)" to="(400,880)"/>

<wire from="(390,830)" to="(390,870)"/>

<wire from="(390,870)" to="(400,870)"/>

<wire from="(430,610)" to="(490,610)"/>

<wire from="(440,450)" to="(450,450)"/>

<wire from="(450,450)" to="(450,480)"/>

<wire from="(450,480)" to="(490,480)"/>

<wire from="(450,890)" to="(490,890)"/>

<wire from="(460,280)" to="(460,520)"/>

<wire from="(460,520)" to="(460,650)"/>

<wire from="(460,520)" to="(490,520)"/>

<wire from="(460,650)" to="(460,930)"/>

<wire from="(460,650)" to="(490,650)"/>

<wire from="(460,930)" to="(490,930)"/>

<wire from="(470,250)" to="(470,500)"/>

<wire from="(470,500)" to="(470,630)"/>

<wire from="(470,500)" to="(490,500)"/>

<wire from="(470,630)" to="(470,910)"/>

<wire from="(470,630)" to="(490,630)"/>

<wire from="(470,910)" to="(490,910)"/>

<wire from="(550,480)" to="(570,480)"/>

<wire from="(550,610)" to="(580,610)"/>

<wire from="(550,890)" to="(590,890)"/>

<wire from="(570,350)" to="(570,370)"/>

<wire from="(570,350)" to="(640,350)"/>

<wire from="(570,370)" to="(570,410)"/>

<wire from="(570,370)" to="(670,370)"/>

<wire from="(570,410)" to="(570,470)"/>

<wire from="(570,410)" to="(660,410)"/>

<wire from="(570,470)" to="(570,480)"/>

<wire from="(570,470)" to="(660,470)"/>

<wire from="(570,480)" to="(570,530)"/>

<wire from="(570,530)" to="(570,660)"/>

<wire from="(570,530)" to="(670,530)"/>

<wire from="(570,660)" to="(570,700)"/>

<wire from="(570,660)" to="(670,660)"/>

<wire from="(570,700)" to="(570,760)"/>

<wire from="(570,700)" to="(660,700)"/>

<wire from="(570,760)" to="(660,760)"/>

<wire from="(580,340)" to="(580,420)"/>

<wire from="(580,340)" to="(640,340)"/>

<wire from="(580,420)" to="(580,480)"/>

<wire from="(580,420)" to="(660,420)"/>

<wire from="(580,480)" to="(580,570)"/>

<wire from="(580,480)" to="(660,480)"/>

<wire from="(580,570)" to="(580,610)"/>

<wire from="(580,570)" to="(660,570)"/>

<wire from="(580,610)" to="(580,620)"/>

<wire from="(580,620)" to="(580,710)"/>

<wire from="(580,620)" to="(670,620)"/>

<wire from="(580,710)" to="(580,770)"/>

<wire from="(580,710)" to="(660,710)"/>

<wire from="(580,770)" to="(660,770)"/>

<wire from="(590,330)" to="(590,380)"/>

<wire from="(590,330)" to="(640,330)"/>

<wire from="(590,380)" to="(590,440)"/>

<wire from="(590,380)" to="(660,380)"/>

<wire from="(590,440)" to="(590,500)"/>

<wire from="(590,440)" to="(670,440)"/>

<wire from="(590,500)" to="(590,580)"/>

<wire from="(590,500)" to="(670,500)"/>

<wire from="(590,580)" to="(590,630)"/>

<wire from="(590,580)" to="(670,580)"/>

<wire from="(590,630)" to="(590,670)"/>

<wire from="(590,630)" to="(660,630)"/>

<wire from="(590,670)" to="(590,730)"/>

<wire from="(590,670)" to="(660,670)"/>

<wire from="(590,730)" to="(590,790)"/>

<wire from="(590,730)" to="(670,730)"/>

<wire from="(590,790)" to="(590,890)"/>

<wire from="(590,790)" to="(670,790)"/>

<wire from="(600,320)" to="(600,550)"/>

<wire from="(600,320)" to="(680,320)"/>

<wire from="(600,550)" to="(600,590)"/>

<wire from="(600,550)" to="(670,550)"/>

<wire from="(600,590)" to="(600,640)"/>

<wire from="(600,590)" to="(670,590)"/>

<wire from="(600,640)" to="(600,680)"/>

<wire from="(600,640)" to="(670,640)"/>

<wire from="(600,680)" to="(600,800)"/>

<wire from="(600,680)" to="(670,680)"/>

<wire from="(600,800)" to="(670,800)"/>

<wire from="(610,310)" to="(610,390)"/>

<wire from="(610,390)" to="(610,510)"/>

<wire from="(610,390)" to="(670,390)"/>

<wire from="(610,510)" to="(610,740)"/>

<wire from="(610,510)" to="(670,510)"/>

<wire from="(610,740)" to="(670,740)"/>

<wire from="(620,300)" to="(620,450)"/>

<wire from="(620,450)" to="(670,450)"/>

<wire from="(670,340)" to="(680,340)"/>

<wire from="(700,380)" to="(720,380)"/>

<wire from="(700,430)" to="(720,430)"/>

<wire from="(700,490)" to="(730,490)"/>

<wire from="(700,540)" to="(730,540)"/>

<wire from="(700,580)" to="(730,580)"/>

<wire from="(700,630)" to="(740,630)"/>

<wire from="(700,670)" to="(730,670)"/>

<wire from="(700,720)" to="(730,720)"/>

<wire from="(700,780)" to="(740,780)"/>

<wire from="(710,330)" to="(730,330)"/>

<wire from="(720,380)" to="(720,400)"/>

<wire from="(720,400)" to="(750,400)"/>

<wire from="(720,420)" to="(720,430)"/>

<wire from="(720,420)" to="(750,420)"/>

<wire from="(730,330)" to="(730,390)"/>

<wire from="(730,390)" to="(750,390)"/>

<wire from="(730,430)" to="(730,490)"/>

<wire from="(730,430)" to="(750,430)"/>

<wire from="(730,670)" to="(730,690)"/>

<wire from="(730,690)" to="(760,690)"/>

<wire from="(730,710)" to="(730,720)"/>

<wire from="(730,710)" to="(760,710)"/>

<wire from="(740,630)" to="(740,680)"/>

<wire from="(740,680)" to="(760,680)"/>

<wire from="(740,720)" to="(740,780)"/>

<wire from="(740,720)" to="(760,720)"/>

<wire from="(780,560)" to="(850,560)"/>

<wire from="(800,410)" to="(850,410)"/>

<wire from="(810,700)" to="(850,700)"/>

</circuit>

</project>

Related Samples

On ProgrammingHomeworkHelp.com, we offer specialized assistance for Embedded System assignments. Our platform provides a comprehensive range of sample projects that cover essential topics in Embedded Systems, including microcontrollers, real-time operating systems, and hardware-software integration. These expertly crafted samples help students grasp complex concepts and enhance their practical skills. Whether you need guidance on Verilog or other Embedded System subjects, our detailed examples and support are designed to boost your understanding and academic performance. Trust us to be your resource for all Embedded System assignment needs.

Embedded System

Embedded System

Embedded System

Embedded System

Embedded System

Embedded System

Embedded System

Embedded System

Embedded System

Embedded System

Embedded System

Embedded System

Embedded System

Embedded System

Embedded System

Embedded System

C++

Embedded System